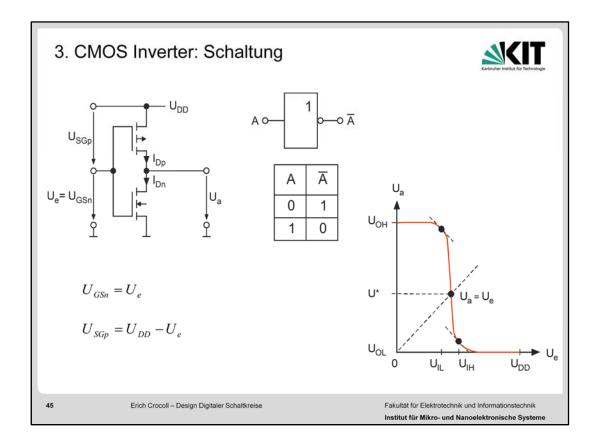

Die einfachste logische CMOS-Schaltung ist der Inverter.

Die beiden Transistoren arbeiten im Gegentaktbetrieb.

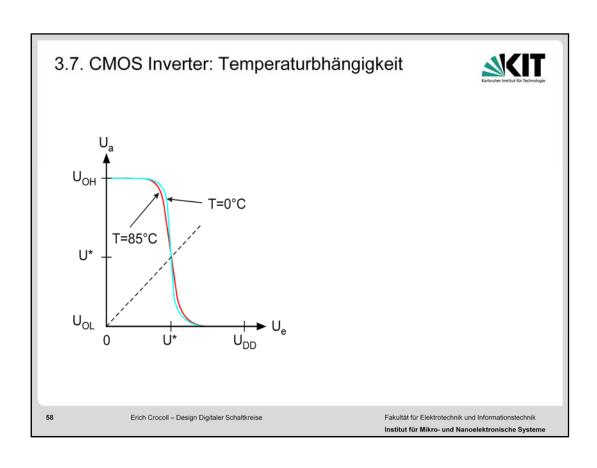

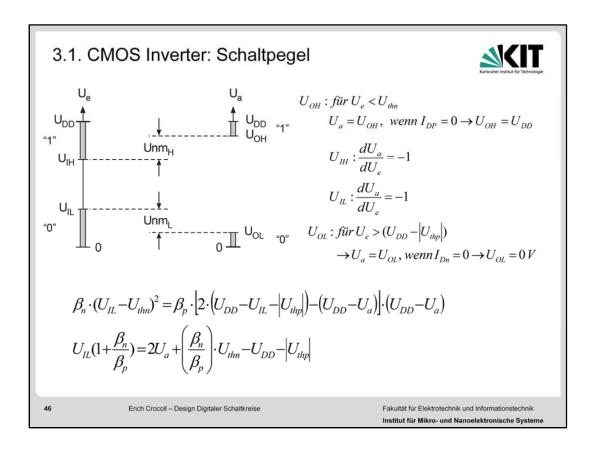

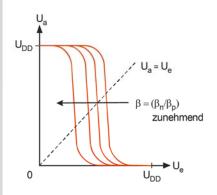

Anhand der Übertragungsfunktion sollen zunächst einige Definitionen betrachtet werden.

Der Schaltpunt ist definiert bei U<sub>a</sub>=U<sub>e</sub>

Die Spannungen  $U_{\rm IL}$  und  $U_{\rm IH}$  werden bestimmt durch die Tangente an die Übertragungsfunktion mit der Steigung -1.

Hier die angesprochenen Gleichungen zur Bestimmung der auf der vorangegangenen Folie.

# 3.1. CMOS Inverter: Berechnungen

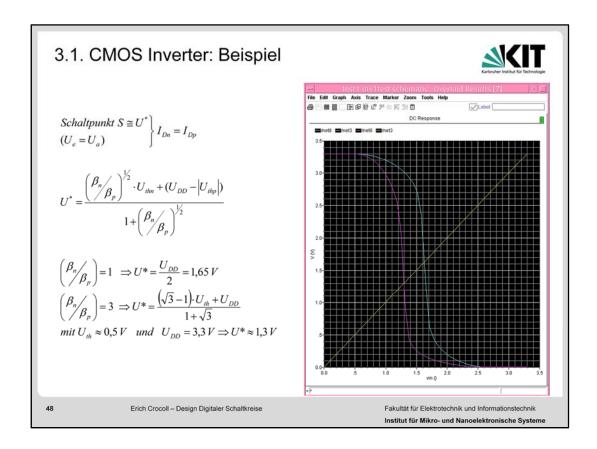

$$\left. \begin{array}{l} Schaltpunkt \; S \cong U^* \\ (U_e = U_a) \end{array} \right\} I_{Dn} = I_{Dp}$$

$$U^* = \frac{\left(\frac{\beta_n}{\beta_p}\right)^{\frac{1}{2}} \cdot U_{thn} + \left(U_{DD} - \left|U_{thp}\right|\right)}{1 + \left(\frac{\beta_n}{\beta_p}\right)^{\frac{1}{2}}}$$

Symetrischer Inverter:

$$U^* = \frac{1}{2} \cdot U_{DD}$$

$$\left(\frac{W}{L}\right)_{p} = \frac{\mu_{n}}{\mu_{p}} \cdot \left(\frac{W}{L}\right)_{n}; \quad \mu_{n} > \mu_{p}$$

wenn

$$U_{thn} = \left| U_{thp} \right| = U_{th}$$

$$\rightarrow \beta_n = \beta_p$$

wenn

$$U_{thn} = |U_{thp}| = U_{th}$$

$\rightarrow \beta_n = \beta_p$

$d.h \ \beta_n' \cdot \left(\frac{W}{L}\right)_n = \beta_p' \cdot \left(\frac{W}{L}\right)_p$

$$da \ \beta_n' = \mu \cdot C_{OX}$$

47 Erich Crocoll – Design Digitaler Schaltkreise Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische System

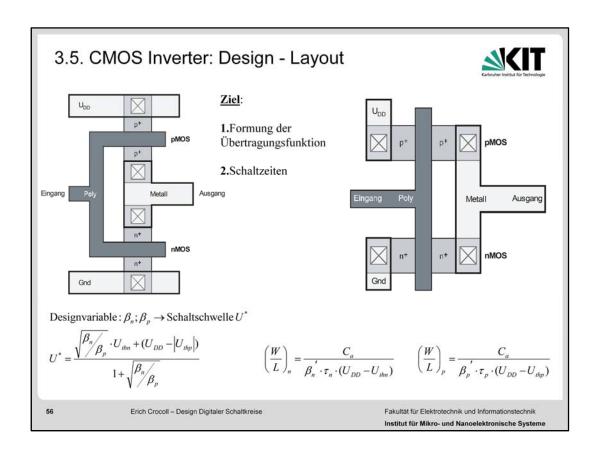

Zur Berechnung des Schaltpunktes wird das so genannte Inverterverhältnis  $\beta = \beta_n/\beta_p$ definiert.

Damit kann U\* bestimmt werden.

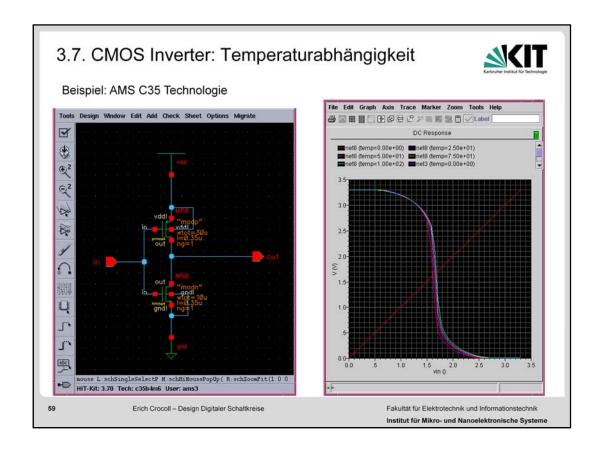

Anhand eines Beispiels soll die Verschiebung des Schaltpunktes aufgezeigt werden.

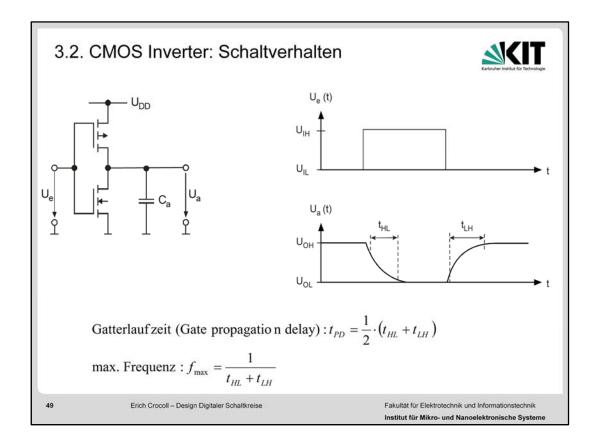

Als nächstes wollen wir das Schaltverhalten näher betrachten.

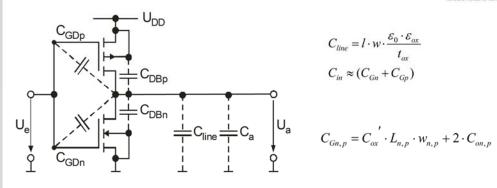

Bei jedem Umschaltvorgang muss die Kapazität  $\mathrm{C_{a}}$ , mit der der Ausgang belastet ist, umgeladen werden.

Die Umladung erfolgt über den Ausgangsstrom und die "internen" Widerstände der Transistoren.

Damit ergibt sich das typische RC-Verhalten.

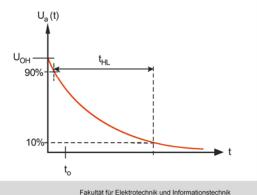

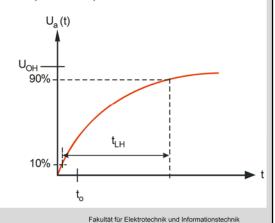

Die Definition der Gatterlaufzeit erfolgt über die 10%-90% Schwellen der Ausgangsspannung.

Damit wird auch die maximal mögliche Taktfrequenz festgelegt.

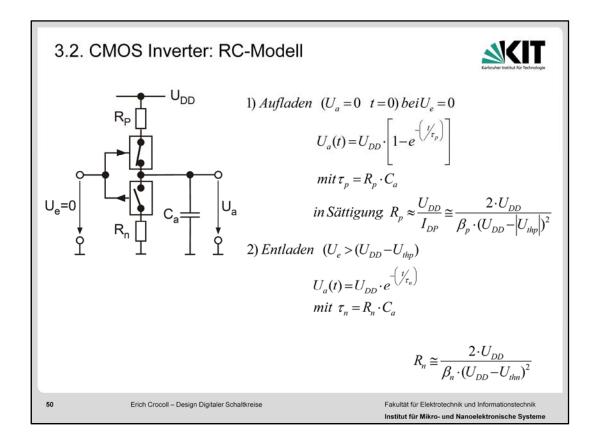

Hier die Umladevorgänge im Detail.

$\boldsymbol{R}_{n}$  und  $\boldsymbol{R}_{p}$  stellen die ohmschen Widerstände im Transistor dar.

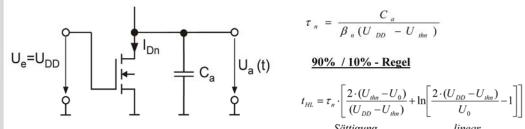

## 3.2. CMOS Inverter: High-to-Low

$$\tau_{n} = \frac{C_{a}}{\beta_{n} (U_{DD} - U_{thn})}$$

$$t_{HL} = \tau_n \cdot \left[ \frac{2 \cdot (U_{thn} - U_0)}{(U_{DD} - U_{thn})} + \ln \left[ \frac{2 \cdot (U_{DD} - U_{thn})}{U_0} - 1 \right] \right]$$

Stitting

$$I_{Dn} = C_a \cdot \frac{dU_a}{dt}$$

;  $da(t=0) = U_{DD}$

$$\begin{split} \boldsymbol{U}_{\boldsymbol{a}}(t) &= \boldsymbol{U}_{\boldsymbol{D}\boldsymbol{D}} - \frac{\beta_n}{2 \cdot \boldsymbol{C}_{\boldsymbol{a}}} \cdot (\boldsymbol{U}_{\boldsymbol{D}\boldsymbol{D}} \ \_\boldsymbol{U}_{\boldsymbol{thm}})^2 \cdot \boldsymbol{t} \\ \ddot{\boldsymbol{U}} bergang \quad & \boldsymbol{S\"{a}ttigung} \quad \rightarrow \boldsymbol{linear} \quad \boldsymbol{Betrieb} \ : \end{split}$$

$$t_0 = \frac{2 \cdot C_a \cdot U_{thn}}{\beta_n \cdot (U_{DD} - U_{thn})^2}$$

$$t_{0} = \frac{2 \cdot C_{a} \cdot U_{thn}}{\beta_{n} \cdot (U_{DD} - U_{thn})^{2}}$$

$$f \ddot{u} r \ t > t_{0} : U_{a}(t) = (U_{DD} - U_{thn}) \cdot \left[ \frac{2 \cdot e^{-\frac{(t - t_{0})}{\tau_{n}}}}{1 + e^{\frac{(t - t_{0})}{\tau_{n}}}} \right]$$

Erich Crocoll – Design Digitaler Schaltkreise

Institut für Mikro- und Nanoelektronische Syst

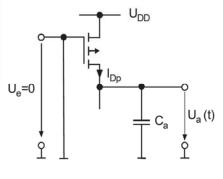

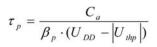

## 3.2. CMOS Inverter: Low-to-High

$$I_{Dp} = C_a \cdot \frac{dU_a}{dt} \quad (U_a(t=0)=0)$$

$$U_a(t) = \frac{\beta_p}{2C_a} \cdot (U_{DD} - \left| U_{thp} \right|)^2 \cdot t$$

$S\ddot{a}ttigung \rightarrow linear \ Betrieb$

$$t_0 = \frac{2 \cdot C_a \cdot \left| U_{thp} \right|}{\beta_p \cdot (U_{DD} - \left| U_{thp} \right|)^2}$$

$$R_p = \frac{1}{\beta_p \cdot (U_{DD} - \left| U_{thp} \right|)}$$

$$\tau_p = C_a \cdot R_p$$

52

Erich Crocoll – Design Digitaler Schaltkreise

Institut für Mikro- und Nanoelektronische Systeme

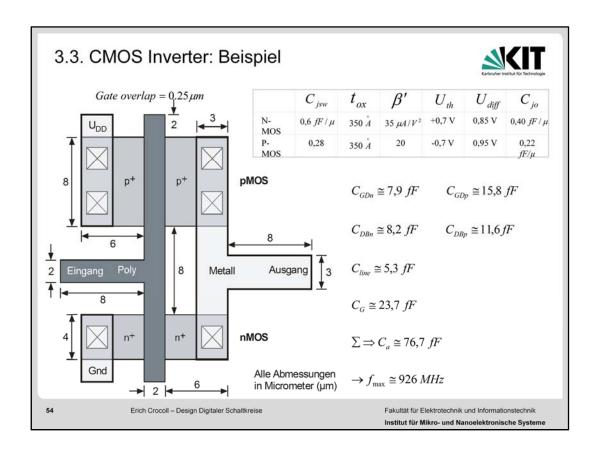

### 3.3. CMOS Inverter: Ausgangskapazität

$$C_{line} = l \cdot w \cdot \frac{\varepsilon_0 \cdot \varepsilon_{ox}}{t_{ox}}$$

$$C_{in} \approx (C_{Gn} + C_{Gp})$$

$$C_{Gn,p} = C_{ox}' \cdot L_{n,p} \cdot w_{n,p} + 2 \cdot C_{on,p}$$

Nichtlineare Kapazitäten!

1)  $U_e \rightarrow H \rightarrow L \rightarrow$  Parallelschaltung aller C!

$$C_{GDn,p} = \frac{1}{2} \cdot C_{ox}' \cdot (w \cdot L)_{n,p} + C_{On,p}$$

$$C_{av} = \frac{1}{(U_{OH} - U_{OL})} \cdot \int_{U_{OL}}^{U_{OH}} \frac{C_{j0} \cdot A}{(1 + \frac{U}{U_{diff}})^m} dU \qquad m = \frac{1}{2} \rightarrow \text{Grundfläche}$$

$$m = \frac{1}{3} \rightarrow \text{Sidewall}$$

53

Erich Crocoll – Design Digitaler Schaltkreise

Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische Syste

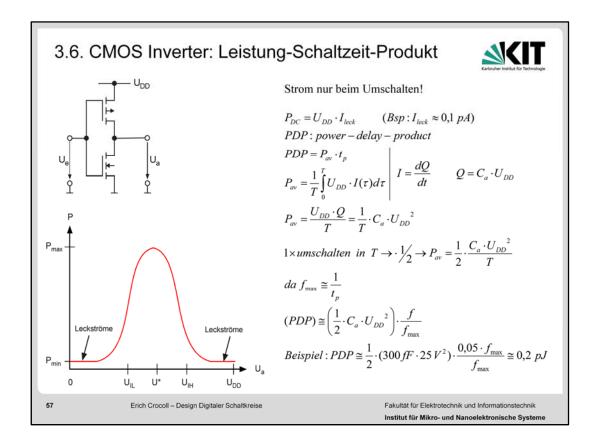

Die statische Verlustleistung  $P_{DC}$  ist im Allgemeinen sehr klein. Der Mittelwert der dynamischen Verlustleistung  $P_{av}$  kann leicht ermittelt werden. Für einen einzelnen Umschaltvorgang muss also eine entsprechende Umschaltenergie aufgewendet werden.